1.3 触发器

你知道吗?计算机和计算器使用触发器来实现其存储功能。多个触发器的组合可以产生一定量的存储容量。

触发器是一种用于数据存储和电路设计的基本构建模块。这些设备对于控制数字信息至关重要,能够存储单个比特的数据。触发器具有多功能性和基础性,能够创建稳定可靠的数字系统。这为探索各种类型的触发器电路奠定了基础,每种电路都有其独特�的特性和应用场景。

什么是触发器?

触发器是一种设计用于存储单个比特二进制数据的设备,本质上是一种基本的存储元件。它会保持其状态(0或1),直到接收到特定的输入信号促使其改变。这一特性使得触发器在数据存储、同步和传输方面变得至关重要,广泛应用于各种数字系统,包括计算机和通信设备。

触发器由逻辑门构成,而逻辑门又是由晶体管组成的。触发器是电子设备存储器的基本构建模块,每个触发器可以存储一位数据。

这些设备也被称为时序逻辑电路。在学习触发器之前,还需要了解以下内容:

- 时序逻辑电路

- 锁存器

触发器具有两个稳定状态,因此它们是双稳态多谐振荡器。这两个稳定状态分别是高电平(逻辑1)和低电平(逻辑0)。

“触发器”这一术语的使用是因为它们可以在控制信号(时钟或使能)的影响下在两个状态之间切换,即可以从一个状态“翻转”到另一个状态,再“翻回”原来的状态。

- 触发器是一种二进制存储设备,因为它们可以存储二进制数据(0或1)。

- 触发器是边沿敏感或边沿触发的设备,即它们对时钟信号的转换敏感,而不是对时钟信号的持续时间或宽度敏感。

- 它们也被称为信号变化敏感设备,这意味着时钟信号电平的变化会触发触发器输出的变化。

- 触发器的工作依赖于时钟脉冲。

- 触发器还用于控制数字电路的功能。它们可以根据状态改变数字电路的操作。

一些最常见的触发器包括SR触发器�(置位 - 复位)、D触发器(数据或延迟)、JK触发器和T触发器。

锁存器与触发器

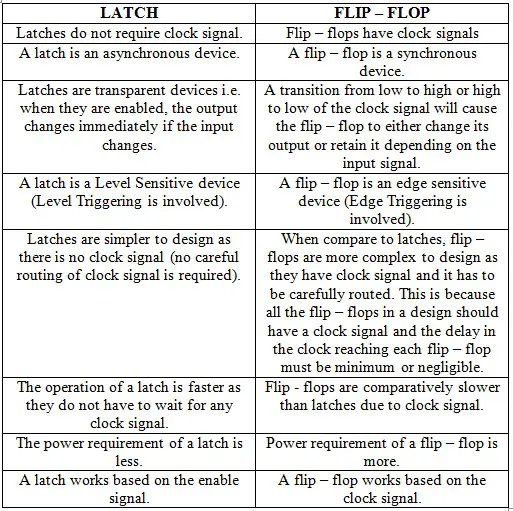

锁存器和触发器都是1位二进制数据存储设备。锁存器和触发器之间的主要区别在于触发机制。锁存器在使能时是透明的,而触发器依赖于时钟信号的转换,即上升沿或下降沿。

现代术语“触发器”通常用于描述有时钟信号的设备,而“锁存器”则用于描述更简单的设备。锁存器和触发器的其他区别如下表所示。

触发器的类型

根据其操作方式,触发器主要有以下四种类型:

- RS触发器

- D触发器

- JK触发器

- T触发器

SR触发器

SR触发器是所有触发器中最基本的一种,其他触发器都是在SR触发器的基础上发展而来的。

SR触发器的符号如下所示。

SR代表“置位”(Set)和“复位”(Reset)。它也可以被称为RS触发器,区别在于RS是反向的SR触发器。

任何触发器都可以使用逻辑门构建。由于与非门和或非门是通用门,因此它们被广泛使用。

以下是使用与非门构建的SR触发器。

SR触发器的真值表

SR触发器的真值表如下所示。

工作原理

从上述真值表可以看出,SR触发器在四种条件下可以被置位或复位。

- 当S = 1且R = 0时,SR触发器被置位。

- 当S = 0且R = 1时,SR触发器被复位。

- 当S = 1且R = 1时,触发器进入不确定状态,这是不允许的。为了避免这种不确定状态,可以通过添加额外的门来设计时钟控制的SR触发器(也称为门控SR触发器)。这种触发器仅在时钟信号为高电平时产生输出。

以下是使用与非门构建的时钟控制SR触发器的电路图。

D触发器

为了避免SR触发器中的不确定状态,可以使用D触发器。这里的“D”代表“数据”(Data)。

D触发器是从SR触发器发展而来的。在时钟控制的SR触发器中,两个输入(S和R)通过反相器连接。

D触发器是最广泛使用的触发器之一。它有一个时钟信号(Clk)作为输入,另一个输入是数据(D)。它有两个输出,这两个输出是互补的。D触发器的符号如下所示。

D触发器的真值表

D触发器的真值表如下所示。

以下是使用与非门(NAND gates)构建的D触发器的电路图。

工作原理

D触发器的工作依赖于时钟信号。

- 当时钟信号为低电平时,触发器的输出不会发生变化,即它会记住先前的状态。

- 当时钟信号为高电平时,如果数据引脚接收到任何数据,它会改变输出的状态。

- 当数据为高电平时,Q被置位为1,而被置位为0;当数据为低电平时,Q被置位为0,而被置位为1。

可以使用D触发器构建主从D触发器。

JK触发器

JK触发器是以电气工程师杰克·基尔比(Jack Kilby)的名字命名的,他发明了集成电路。

JK触发器是SR触发器的改进版本。在这种触发器中,J输入类似于SR触发器的置位输入,K输入类似于SR触发器的复位输入。在SR触发器中不允许的条件(S = R = 1)在JK触发器中被解释为“翻转”命令。

JK触发器具有:

- 两个数据输入J和K。

- 一个时钟信号输入(CLK)。

- 两个输出Q和。

JK触发器的符号如下所示。

JK触发器的真值表

JK触发器的真值表如下所示。

以下是使用逻辑门构建的JK触发器的电路图。它类似于经过改进的与非门SR触发器。

工作原理

- 当J为低电平且K为低电平时,Q返回其先前状态值,即保持当前状态。

- 当J为低电平且K为高电平时,触发器处于复位状态,即Q = 0, = 1。

- 当J为高电平且K为低电平时,触发器处于置位状态,即Q = 1, = 0。

- 当J为高电平且K为高电平时,触发器处于翻转状态。这意味着输出将与先前状态值互补。

T触发器

T触发器也被称为“翻转触发器”。翻转是指在时钟输入信号存在的情况下,将输出切换到先前状态的补码。

T触发器具有:

- T输入。

- 一个时钟信号输入(CLK)。

- 两个输出Q和。

T触发器的符号如下所示。

我们可以使用其他类型的触发器来构建T触发器。

- SR触发器:通过将SR触发器的输出反馈连接到输入(S和R)来实现。

- D触发器:将D触发器的反向输出连接到其数据输入端,作为反馈路径。

- JK触发器:通过将JK触发器的J和K输入端合并为一个输入,可以设计出T触发器。

T触发器的真值表

T触发器的真值表如下所示。

以下是使用与非门构建的JK触发器改造而成的T触发器的电路图。

工作原理

T触发器的工作原理如下:

- 当T输入为低电平时(T = 0),T触发器的下一状态与当前状态相同,即保持当前状态。

- 如果当前状态为0,则下一状态仍为0。

- 如果当前状态为1,则下一状态仍为1。

- 当T输入为高电平时(T = 1),T触发器的下一状态将翻转,即在时钟信号的作用下,下一状态为当前状态的反相。

- 如果当前状态为0,则下一状态变为1。

- 如果当前状态为1,则下一状态变为0。

触发器的应用

触发器被广泛应用于以下领域:

- 寄存器:由于触发器具有两个稳定状态,我们将其用于寄存器等存储元件中,以实现数据存储。寄存器通常用于电子设备,如计算机。

- 计数器:多个相互连接的触发器可以组成计数器,用于统计事件的发生次数(递增或递减)。

- 频率分频:触发器被用作频率分频电路,将输入频率精确地减半。频率分频电路用于调节电子电路的频率。

- 数据传输:我们使用移位寄存器(一种特殊类型的寄存器)来按特定顺序将数据从一个触发器传输到另一个触发器。